Product Summary

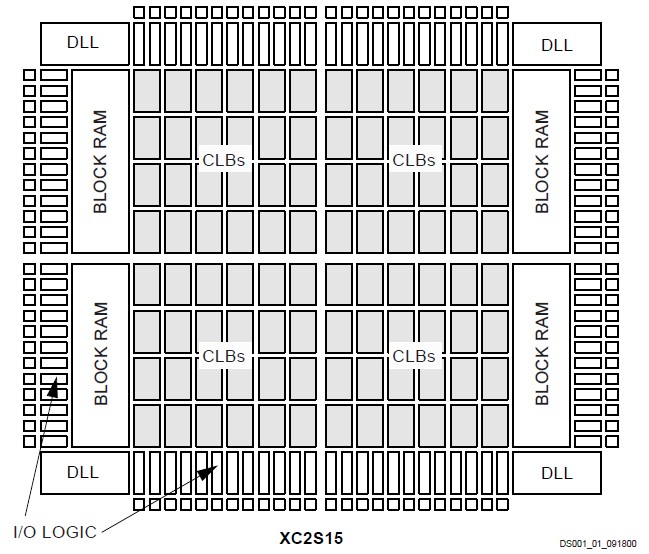

The XC2S200-6PQG208C is a Field-Programmable Gate Array. It gives users high performance, abundant logic resources, and a rich feature set, all at an exceptionally low price. The six-member family offers densities ranging from 15,000 to 200,000 system gates. System performance is supported up to 200 MHz. Features of the XC2S200-6PQG208C include block RAM (to 56K bits), distributed RAM (to 75,264 bits), 16 selectable I/O standards, and four DLLs. The XC2S200-6PQG208C is a superior alternative to mask-programmed ASICs. The FPGA avoids the initial cost, lengthy development cycles, and inherent risk of conventional ASICs.

Parametrics

XC2S200-6PQG208C absolute maximum ratings: (1)VCCINT Supply voltage relative to GND: –0.5 to 3.0 V; (2)VCCO Supply voltage relative to GND: –0.5 to 4.0 V; (3)VREF Input reference voltage: –0.5 to 3.6 V; (4)VIN Input voltage relative to GND 5V tolerant I/O: –0.5 to 5.5 V; No 5V tolerance: –0.5 to VCCO+0.5 V; (5)VTS Voltage applied to 3-state output 5V tolerant I/O: –0.5 to 5.5 V; No 5V tolerance: –0.5 to VCCO+0.5 V; (6)TSTG Storage temperature (ambient): –65 to +150 ℃; (7)TJ Junction temperature: - +125 ℃.

Features

XC2S200-6PQG208C features: (1)SelectRAM hierarchical memory: 16 bits/LUT distributed RAM; Configurable 4K bit block RAM; Fast interfaces to external RAM; (2)Fully PCI compliant; (3)Low-power segmented routing architecture; (4)Full readback ability for verification/observability; (5)Dedicated carry logic for high-speed arithmetic; (6)Efficient multiplier support; (7)Cascade chain for wide-input functions; (8)Abundant registers/latches with enable, set, reset; (9)Four dedicated DLLs for advanced clock control; (10)Four primary low-skew global clock distribution nets; (11)IEEE 1149.1 compatible boundary scan logic.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

XC2S200-6PQG208C |

|

IC SPARTAN-II FPGA 200K 208-PQFP |

Data Sheet |

|

|

||||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|

XC2S100 |

Other |

|

Data Sheet |

Negotiable |

|

||||||

|

XC2S100-5FG256C |

|

IC FPGA 2.5V 600 CLB'S 256-FBGA |

Data Sheet |

|

|

||||||

|

XC2S100-5FG256I |

|

IC FPGA 2.5V I-TEMP 256-FBGA |

Data Sheet |

|

|

||||||

|

XC2S100-5FG456C |

|

IC FPGA 2.5V 600 CLB'S 456-FBGA |

Data Sheet |

|

|

||||||

|

XC2S100-5FG456I |

|

IC FPGA 2.5V I-TEMP 456-FBGA |

Data Sheet |

Negotiable |

|

||||||

|

XC2S100-5FGG256C |

|

IC SPARTAN-II FPGA 100K 256-FBGA |

Data Sheet |

|

|

||||||

(China (Mainland))

(China (Mainland))